Protokollanalyse

SA ist die Lösung von Teledyne LeCroy für Serial ATA-TestsTracer/Trainer:innen System. Diese All-in-One-Testplattform bietet Traffic-Generierung mit integrierter Protokollanalyse. Der Generator unterstützt sowohl die host- als auch die geräteseitige Emulation. Es ist ein vollständig integriertes System, das nur geringfügig größer als ein Laptop ist, wodurch es sowohl für den Einsatz im Labor als auch im Feld geeignet ist.

SATracer bietet alles, was für die Serial ATA-Analyse benötigt wird, einschließlich Echtzeit-Hardware-Triggerung und Filterung der kritischen Komponenten des Serial ATA-Datenverkehrs. Die Expert Analysis-Software von Teledyne LeCroy vereinfacht den gesamten Debugging-Prozess, indem zusammenklappbare, farbcodierte Pakete verwendet werden, um Befehle, FISs und Primitive darzustellen. Dies bietet Point-and-Click-"Drilldown" zu Details auf niedrigerer Ebene zusammen mit der Benutzerfreundlichkeit und dem Verständnis, für die Teledyne LeCroy bekannt ist.

Übersicht über SATA (Serial ATA).

Die Speicherbranche befindet sich mitten in einem groß angelegten Übergang von Parallel ATA, der dominierenden Desktop-Speicherschnittstelle, zu Serial ATA. Diese Migration spiegelt einen breiteren Übergang in der gesamten Branche zu seriellen Technologien für computerbasierte Kommunikation wider. Angetrieben hauptsächlich von niedrigeren Spannungen und Kosten, die in zukünftigen Chipsätzen erforderlich sind, ist Serial ATA bereit. Zur branchenweiten Einführung. Die Spezifikation wahrt sorgfältig die Softwarekompatibilität mit dem Parallel ATA-Befehlssatz. Darüber hinaus bietet es kleinere, dünnere und kostengünstigere Kabel, die auch Kompatibilität auf der physikalischen Ebene mit dem aufkommenden Serial Attached SCSI (SAS)-Standard bieten.

Eigenschaften

Leistung - Parallel ATA ist nicht skalierbar, um mehrere weitere Geschwindigkeitsverdopplungen zu unterstützen, und nähert sich seiner Leistungskapazität. Serial ATA hingegen definiert eine Roadmap ab 1.5 Gigabit pro Sekunde (entspricht einer Datenrate von 150 MB/s) bis hin zu 3.0 Gigabit pro Sekunde (300 MB/s).

Niedrigere Spannung - Die 5-Volt-Signalisierungsanforderung von Parallel ATA wird immer schwieriger zu erfüllen sein, da die Industrie weiterhin Chip-Core-Spannungen reduziert. Serial ATA ist besser auf zukünftige Fertigungsprozesse ausgerichtet. Es reduziert Signalspannungen auf etwa 250 Millivolt (1/4 Volt).

Pin-Anzahl - Derzeit hat die parallele ATA-Schnittstelle 26 Signalstifte, die in den Schnittstellenchip gehen. Serial ATA verwendet nur 4 Signalpins, wodurch die Pineffizienz verbessert und eine hochintegrierte Chipimplementierung ermöglicht wird.

Verbesserte Verkabelung - Sperrige parallele ATA-Flachbandkabel enthalten einen 40-poligen Header-Anschluss. Serial ATA führt ein dünnes, flexibles Kabelschema ein, das längere Kabel und einen verbesserten Luftstrom innerhalb des Gehäuses bietet.

Software-kompatibel - Serial ATA ist auf Registerebene mit Parallel ATA kompatibel. Das bedeutet, dass Serial ATA keine Änderungen an bestehender Software und Betriebssystemen erfordert, um zu funktionieren, und es bietet Abwärtskompatibilität mit bestehenden Betriebsumgebungen.

SAS-Kompatibilität - Ein wesentliches Merkmal von Serial ATA ist die Erwartung, dass SATA formfaktorkompatibel mit Serial Attached SCSI sein wird. SATA-Laufwerke werden direkt an Serial-Attached-SCSI-Anschlüsse angeschlossen und funktionieren, sofern vom System unterstützt, transparent als SATA-Gerät. Dadurch können Systeme bereitgestellt werden, die entweder Serial Attached SCSI-Laufwerke für ihre hohe Leistung oder SATA-Laufwerke verwenden können, die eine Speicherplattform mit niedrigeren Kosten pro Megabyte bieten.

Architektur

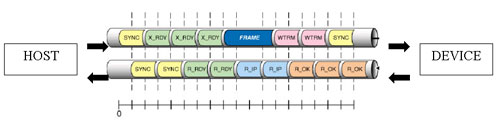

Serial ATA ist ein Vollduplex-Protokoll. Es gibt einen kontinuierlichen Signalfluss von jedem Gerät, das sich den Bus entlang bewegt. Das Gerät und der Host senden (TX) und empfangen (RX) gleichzeitig.

Das bidirektionale Verkehrsmuster eliminiert den Bedarf an Bus-Aushandlungs-Overhead

Datenzeichen vs. Primitive - Primitive sind die einfachsten Elemente innerhalb des Serial ATA-Protokolls. Primitive sind 32-Bit-DWORDs, die verwendet werden, um die Steuerung der Funktionen der seriellen Leitung (X_RDY, CONT usw.) zu initiieren. Zusätzlich zu diesen „Handshaking“- und Flusssteuerungssignalen werden Primitive auch verwendet, um Benutzerdaten abzugrenzen oder zu „rahmen“.

Rahmeninformationsstruktur (FIS) - Ein Frame ist eine unteilbare Informationseinheit, die zwischen einem Host und einem Gerät ausgetauscht wird. Ein Rahmen besteht aus einem SOF-Grundelement, einer Rahmeninformationsstruktur (FIS), einem CRC, der über den Inhalt des FIS berechnet wird, und einem EOF-Grundelement. Ein FIS ist die Benutzernutzlast eines Rahmens; Ein Frame ist eine Gruppe von Dwords, die Informationen zwischen Host und Gerät übertragen, wie zuvor beschrieben.

Die obige Abbildung zeigt die logische Struktur der Serial ATA-Hierarchie zusammen mit SATracer's Darstellung des Protokolls, wie es in Teledyne LeCroy Trace™ angezeigt wird.

Links

Quellen: Intel Entwicklungslabors; Serial ATA-Spezifikation 1.0 Copyright 2001; Serial ATA-Arbeitsgruppe